■ 제품필수정보

| 제조사 |

Microchip |

| 제조사품명 |

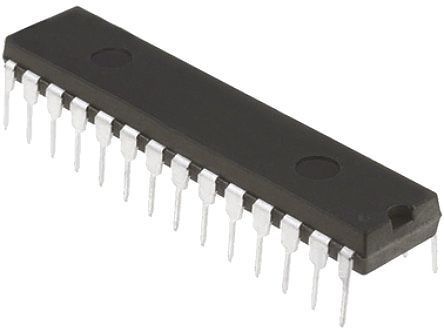

DSPIC33EV256GM002-I/SP |

| 간략설명 |

DSPIC33EV256GM002-I/SP Microchip, 16bit Digital Signal Processor 70MHz 256 kB Flash 28-Pin PDIP |

■ 제품사양

최대 주파수 = 70MHz Device Million Instructions per Second = 70MIPS

데이터 버스 = 16bit

RAM 크기 = 16 kB Instruction Set Architecture = C

프로그램 메모리 크기 = 256 kB Program Memory

타입 = Flash

장착형태 = Through Hole

패키지 = PDIP

핀수 = 28

일반 작동 공급 전압 = 4.5 to 5.5 V Number of UART Channels = 2 ADC Resolution = 12 bit, 10bit dsPIC33EVxxxGM00x/10x 16-Bit Digital Signal Controllers. Microchip ??s dsPIC33EV family of 16-bit Digital Signal Controllers (DSCs) features a 70 MIPS dsPIC® DSC core with enhanced on-chip features. Capable of operating in harsh environments these devices are suitable for appliance and automotive applications. Rich peripheral integration includes SENT (Single-Edge Nibble Transmission-Transmit/Receive), High Speed PWMs, OP Amps and Error Correcting Code Flash for increased reliability and safety. The performance offered by the dsPIC33EV family of MCUs allows them to be incorporated into the design of high-performance, precision motor control systems that are more energy efficient. They can be used to control BLDC, permanent magnet synchronous, AC induction and stepper motors. Microcontroller Features. 70 MHz Max. CPU Speed Code-Efficient (C and Assembly) Architecture 16-Bit Wide Data Path Two 40-Bit Wide Accumulators Single-Cycle (MAC/MPY) with Dual Data Fetch Single-Cycle, Mixed-Sign MUL plus Hardware Divide 32-Bit Multiply Support Intermediate Security for Memory - Provides a Boot Flash Segment in addition to the existing General Flash Segment Error Code Correction (ECC) for Flash Added Two Alternate Register Sets for Fast Context Switching. Clock Management Features. Internal, 15% Low-Power RC (LPRC) ??32 kHz Internal, 1% Fast RC (FRC) ??7.37 MHz Internal, 10% Backup RC (BFRC) ??7.37 MHz Programmable PLLs and Oscillator Clock Sources Fail-Safe Clock Monitor (FSCM) Additional Fail-Safe Clock Monitor Source (BFRC), Intended to Provide a Clock Fail Switch Source for the System Clock Independent Watchdog Timer (WDT) System Windowed Watchdog Timer (DMT) Fast Wake-Up and Start-Up. Power Management Features. Low-Power Management modes (Sleep, Idle and Doze) Power Consumption Minimized Executing NOP String Integrated Power-on Reset (POR) and Brown-out Reset (BOR) 0.5 mA/MHz Dynamic Current (typical) 50 μA at +25°C IPD Current (typical). Peripheral Features. Up to Six Pulse-Width Modulation (PWM) Outputs (three generators) Configurable Analogue to Digital Converter (ADC) Module Up to 4 Operational Amplifiers Up to 5 Comparators Charge Time Measurement Unit (CTMU) - Supports mTouch??capacitive touch sensing Five 16-bit Timers Two 32-bit Timers Four Output Capture modules Configurable as Timers/Counters Four Input Capture modules Two Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) Two SPI Modules One I2C Module with SMBus Support